LPC176x/175x 12位ADC設計指導--LPC176x/175x 12-bit ADC design guidelines

文檔信息

關鍵字

LPC1700,LPC175X,LPC176X,12位ADC

摘要

PCB設計參考,軟件測試LPC1768 12位 ADC

1.簡介

基于ARM Cortex M3內核,LPC175X/6X包含一個12位模數轉換模塊(ADC):8引腳多路輸入,轉換速率達200KHZ,多個結果寄存器。此12位ADC可以和GPDMA控制器同時工作。

使用12位ADC設計系統,需要比傳統的使用NXP LPC系列產品解決方案更細心。

作為對照,在10位ADC系統中使用3.3V參考電壓,每一個轉換值均不同于3.2mV(3.3V/1024)。在12位ADC中,LSB(最低有效位)的值低至0.8mV。對比3.2mV和0.8mV, 可以明顯看出降噪技術在系統設計中有重要的作用,無論是原理圖,還是PCB的設計。該應用手冊,可以作為PCB板設計的指導,包含了一個參考設計和軟件工程,用戶可以用來測試LPC1700 12位ADC。一些測試情況也包含在里面,可以說明一些影響轉換結果的因素。

2.PCB板設計參考

本文檔提供了一個完整的板子設計案例。用戶可以使用這個設計作為他們自己設計的起點。這個案例使用的軟件叫作:Eagle布局編輯器5.4.0(Eagle Layout Editor Version 5.4.0 ),整個工程,包括原理圖、布局和BOM,都在本文檔中。

該板的主要目的在于ADC的測試;所有的ADC通道都能測試。兩個BNC連接器,用于輸入外部信號(或外部電源提供的固定電壓);兩個電位計,提供一個可調節的電壓,可連接到模擬輸入線(通過跳線選擇模擬通道輸入)。

這個板可以選擇不同的電源。從一個通用源,就可以獲得模擬或數字電源:使用USB連接器(PC供電)或者外部電源(提供3.3V外部電壓)。另一種可行方案是為每一個源(模擬或數字)提供獨立電源,甚至可以從一個獨立的電源提供VREF(Voltage reference for the ADC,ADC基準電壓)。通過跳線,用戶可以選擇想要的配置。

調試以及FLASH編程都有一個JTAG/SWD調試端口。通過COM0連接器(通過跳線選擇相應的UART0),FLASH編程也可以使用ISP。UART1也是通過跳線選擇。板上有RESET和ISP按鍵,一個通用LED。板上所有的GPIO引腳均可用。

板子布局與符錄中的設計指導相對應。為了降低成本,采用了雙層設計。底層作為接地層(ground planes)。模擬和數字接地層可用,一對跳線可以選擇不同的配置。兩個地端連接到一個點上,或通過一個choke相連,也有可能是自獨立。這些選項可以讓用戶體驗不同的情況,并比較結果的差異。

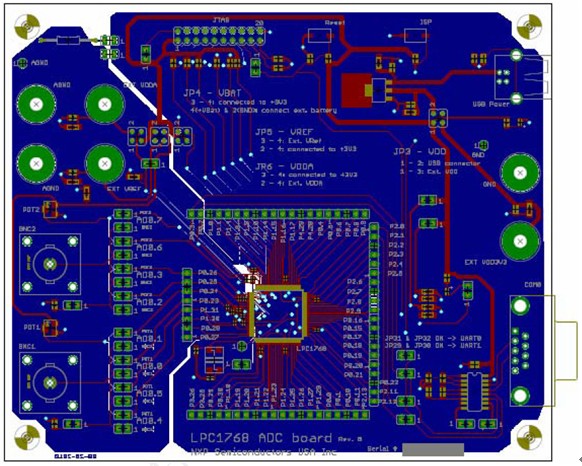

頂層主要用于電源和信號的走線(traces)。數字信號(特別是高頻或者大電流部件上的)位于數字地端,遠離模擬區域。模擬相關的部件(BNC連接器,模擬電位器,模擬電壓的跳線和連接器)位于板的左邊緣,形成一個“模擬島”。數字相關的部件位于板的另一端。圖1所示為板的最后布局。如圖所示,所有的跳線都在板上注了相應的標簽。

圖1 LPC1768 ADC 電路板布局

3. 軟件測試

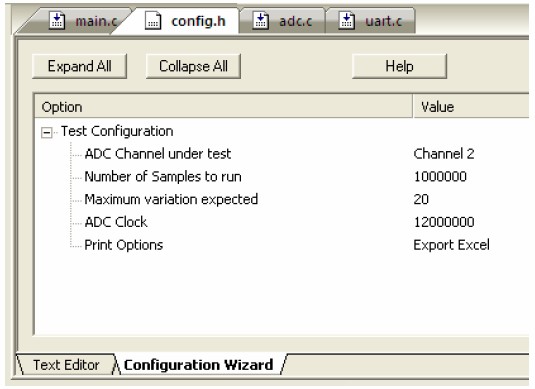

為了測試這塊板,本文檔提供了相應的軟件。此工程使用Keil MDK version 4.03(可以使用免費的評估版本)。用這個軟件,用戶可以選擇測試的ADC通道,以及示例的號碼。其他參數,像ADC時鐘,也可以設置。

理想情況下,所選擇的通道輸入一個固定電壓時,所有的示例都會返回相同的值。實際中,可能會出現干擾或電壓不穩,而導致結果出現偏差。最后的結果是出現幾個接近的值,而且不會是同一個值。只要減少干擾、改進電源質量,就能把誤差限定在一個較小的范圍。

因為軟件使用一個數列來確保不同的轉換結果,所以應該先定義這個數列。代碼中命名為“Maximum variation expected”的參數,作為這個數列的初始值,默認值為20,能夠滿足大多數情況。另兩個變量限制了值的范圍(最大和最小值),所以用戶可以對這個參數作一些調整。

另一個參數定義了打印的選項。所有的參數都可以在config.h文件中找到,可以在Keil Configuration Wizard(Keil配置向導)中編輯,如圖2所示。

圖2 軟件配置參數

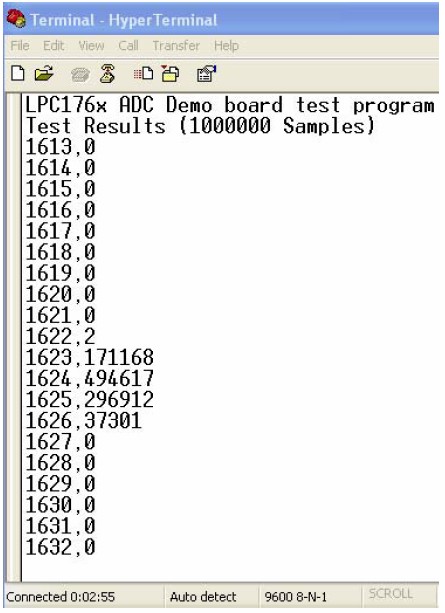

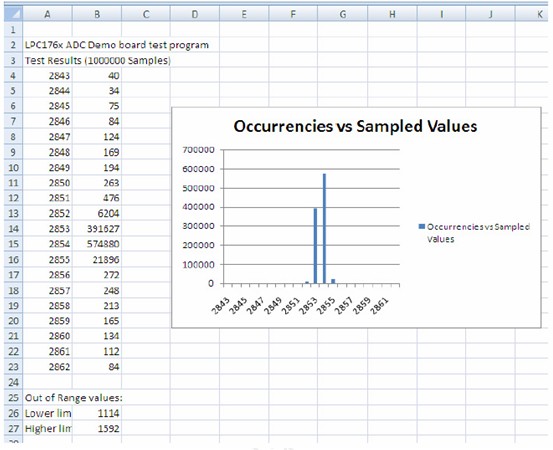

只要板編程通過,就可以通過終端程序(HyperTerminal program)查看程序的信息。使用終端,需要用串口線連接ADC板(COM0)和PC串口,啟動終端程序的參數為:9600,8,N,1,N。初始化完成之后,程序啟動ADC取樣,結果顯示在終端程序的屏幕上。如果在配置向導中選擇了“Export Excel”,則取樣值以及相應的序號將出現在屏幕上。見圖3。

圖3 終端顯示的結果

獲取這些信息,并保存為文件,文件后綴為“csv”。這個文件就可以用微軟的Excel打開,文件上的值就會分兩列顯示。這樣,就可以很容易的生成相應的柱形圖,見圖4。

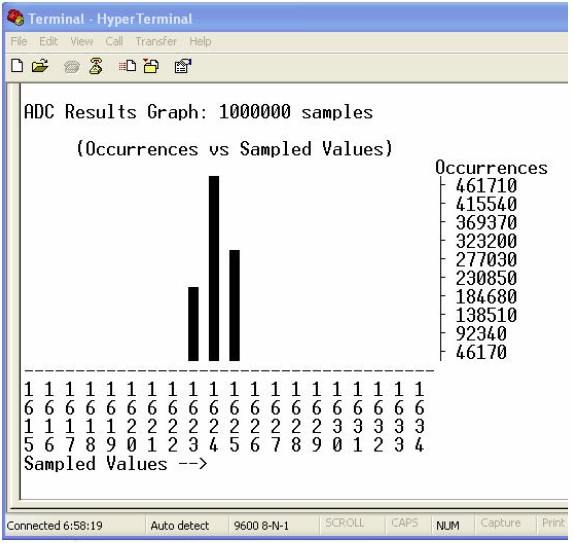

配置中的另一個打印選項“Plot Values”,結果值可以在終端屏幕上直接顯示為圖表,用戶就可以快速評估測試結果而不需要額外的輸出這些值。見圖5。

注意:使用JTAG調試時會影響結果,詳見4.2。

圖5 終端顯示柱形圖

4.運行測試

在這一部分,提供了不同的測試情況,以及相應的結果。

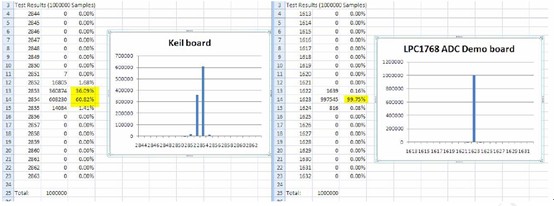

4.1 Keil MCB1700 和 LPC1768 ADC 評估板的比較

基準測試在MCB1700 Keil 板和LPC1768 ADC 評估板上進行,圖六為測試結果。

如上圖所示,LPC1768 ADC 評估板能夠把99.75%的取樣轉為同一個值,干擾達到最小,由此可見,ADC的性能好于Keil板。這個結果證實了LPC1768 ADC 評估板的設計的優異性。

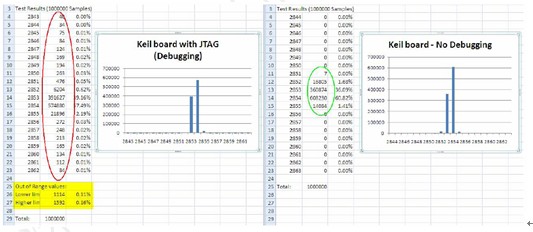

4.2 JTAG 調試的影響

提醒用戶,在某些情況下,使用JTAG調試可能會對結果產生不良影響,有時會引入額外的干擾導致一些故障(值會超出范圍,包括兩個峰值0x000和0xfff)。圖7為JTAG的影響。

圖7 JTAG的影響

如圖7所示,JTAG會引入額外的干擾,擴大了樣值的范圍。

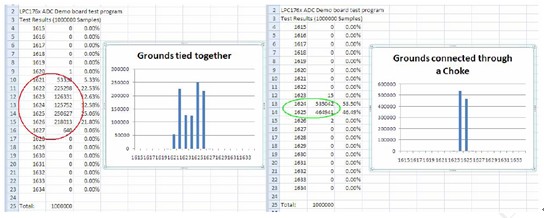

4.3 地端的影響

該板提供了兩個不同的地端,一個是模擬區域,另一個是數字區域。在多數情況下,只要一個系統級的地端作為參考點,所以有時就需要把兩個地端連接起來。

直接連接兩個地端可能會導致數字端引入干擾到模擬區域。使用感應器(inductor)或者choke連接兩個地端,由于感應器的濾波作用,數字端的干擾達到最小化,見圖8。

圖8 地端的影響

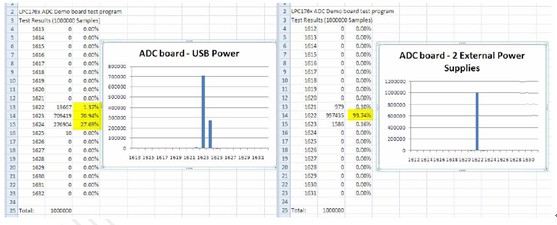

4.3 電源質量的影響

另一個干擾源就是電源。電源電壓的波動,會極大的影響ADC性能。為每一塊區域(數字和模擬)提供獨立的電源往往能得到更好的結果,見圖9。

圖9 電源質量對結果的影響

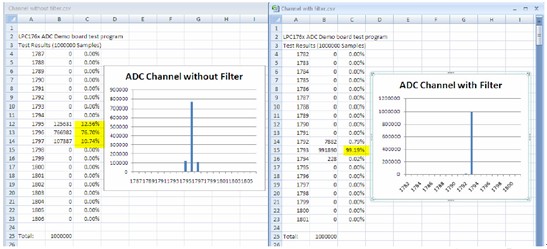

4.4 ADC通道輸入濾波的影響

低通濾波器可以大大的改善結果,如圖10所示。LPC1768 ADC 評估板在每一個ADC通道輸入的低通濾波器上都有電容器。并不是所有板上的濾波器都起作用,這個測試顯示了起作用的濾波器的改進作用。另一些情況,使用去鋸齒濾波器(和相應激活的部件)能夠進一步改善測試結果。

圖10 低通濾波器的影響

5. 結論

設計一個精確的、可靠的12位ADC需要在PCB布局、電源設計和去耦上下功夫。PCB板的走線應該遵循本應用手冊的設計原則,以減少干擾的影響。每一個區域使用一個獨立的地端是一個有效的方法。如果可能,為數字和模擬區域提供獨立的電源也可以獲得好的結果。最后,濾波器也是一個不可或缺的部件。

6. 附錄A 設計指導

下面的指導提供了一個通用的最好的PCB布局實例:包含高頻或大電流電路,模擬和數字電路相結合。

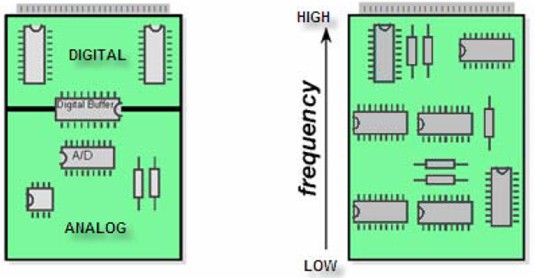

6.1 組件位置

- 模擬電路與數字電路相互獨立,以隔絕轉換的干擾。

- 干擾和高頻組件應該布置在靠近連接器或電源的位置。

圖11 推薦的組件布局

6.2 地端方案

(1)每一個區域(模擬或數字)使用獨立的地端

(2)使用接地層(如果可能)

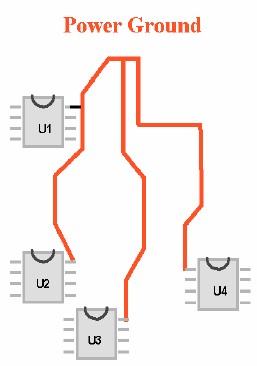

(3)如果沒有接地層,地的連接使用“星”布局:

- 如果可能,使用獨立的地電流回路

- 低電流/低速信號設備共用回路(參看U1&U2)

- 走線盡可能寬

- 避免地端短路

- 數字電流不要通過模擬器件

- 大電流和高速電流不要通過模擬和低速區域

- 走線盡可能的短,這樣有效電感和電阻就能最小

- 如果有接地層,盡可能多使用它作為電流回路

- 為模擬部分設計獨立的接地層,用空隙分離模擬和數字的接地層

- 避免板的頂部和底部可能出現的短路

- 在接地層,地電流盡可能最短;如果信號走線要插入板的接地層旁邊,走線要最短,并與地電流回路相垂直。

- 當模擬和數字區域使用獨立地端,則只有一個點作為系統的地,兩個地端要連接在一起作為一個信號點;一個ferrite bead或感應器在這個連接部位去耦。

圖12 星形布局

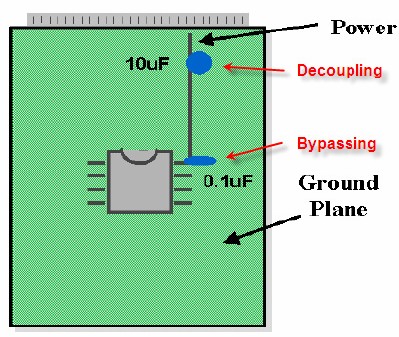

6.3 旁路和去耦電容

(1) 旁路電容為高頻電流提供低阻抗通路,減少了電源線的電流干擾。通常,0.1uF就足夠了,并盡可能的靠近器件。

(2) 去耦電容隔離兩個電路,可以避免干擾從一個電路傳到另一個電路。和一個感應器一起使用,就可以形成一個低通濾波器。10uF就可以了,且靠近電源

圖13 旁路和去耦電容

6.4 電源層

(1)電源層也需要,雖然沒有像接地層那么嚴格。

(2)兩層板,電源層也可以用寬的走線代替(寬度為其他走線的2到3倍)。

6.4 多層板

(1)嚴格和/或復雜的設計就要使用多層板。

(2)這種情況下,強烈建議接地層和電源層使用不同層。

(3)因為很多器件都是SMD,他們的連接就需要外露在板的外部邊緣;這樣,內層就可以專用為電源和接地層,能夠突出電容的優點。

(4)如果多于4層,接地層和電源層高速信號要隔離。低速信號要在外層上。

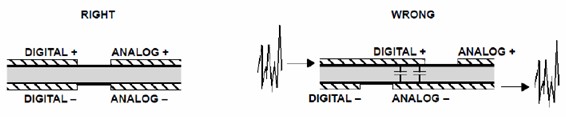

6.5 路由信號

不同的區域(模擬和數字)的信號/電源/地層不要重疊。否則,電容就會把高速數字干擾加到模擬電路。

圖14

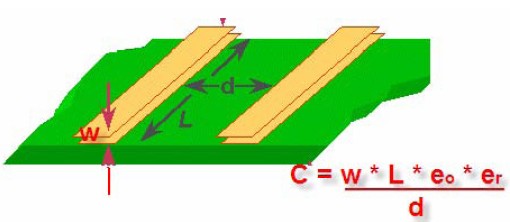

(1) 分離數字信號(特別是高頻、干擾I/O、大電流)和模擬信號。即使是走線和層之間的小電容,也能引起干擾,不僅是低頻,也包括高諧頻。

(2) 高阻抗容易通過電容引入干擾,尤其是電壓變化快的走線,像數字時鐘。為了最小化電容,要加大兩條走線之間的距離,且長度要長,寬度要小。

圖15 推薦走線間的距離

(3) 信號走線(通常)要盡可能的短,以最小化寄生電感和電容。

(4) 避免信號線并排,以減少串擾。如果無法避免,信號線之間應該要留出至少3倍信號線寬度的間隙。

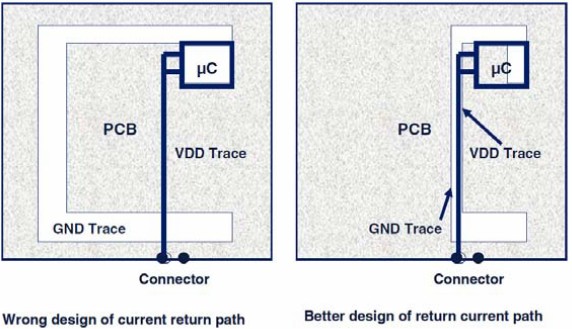

(5) 最小化電源和地走線的回路(如果沒有接地端的話)。

圖16

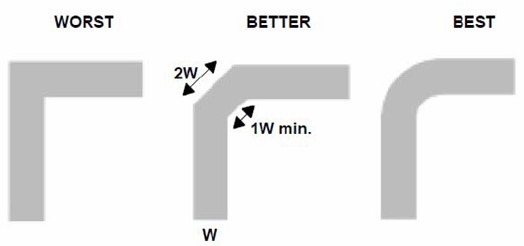

(6) 采用圓形拐角

圖17 采用圓形拐角

完整PDF文檔下載