LPCXpresso環境下的LPC1100低功耗模式和喚醒時鐘

1.簡介

基于ARM Cortex-M0 CPU架構,LPC1100微控制器系列(8/16位應用),高性能、低功耗、簡易指令、存儲器尋址,與現有的8/16架構相比,代碼體積更小。

LPC1100系列外設包括32KB flash 存儲器,8KB數據存儲器,一個C-CAN控制器(LPC11Cxx),一個高速+IIC總線接口,一個RS-485/EI-485UART,兩個SPI接口(SSP特性),4個通用定時器,一個10位ADC,以及42個通用I/0引腳。

LPC11Cxx系列包含片上C-CAN驅動和通過C-CAN在線系統編程flash工具。LPC11C2x系列有一個片上高速CAN收發器。

LPC11xx(L)系列包含片上功率配置部件。

LPC1100系列定位于一系列廣泛的應用,包括eMetering、照明、工業網絡、報警系統以及白色家電。

本文檔介紹了LPC11xx系列,LPC11xx(L)系列和LPC11Cxx系列的各種低功耗模式。進入低功耗模式、喚醒狀態,可以有效降低功耗。本文檔同時提供了一個軟件示例,使用LPC1114 LPCXpresso板進入低功耗模式測量功耗和喚醒時鐘。

本文檔包括以下要點:

- (1) 低功耗模式

- (2) 進入低功耗模式

- (3) 喚醒狀態

- (4) 降低功耗

- (5) LPC1114 LPCXpresso低功耗模式演示

2.低功耗模式

LPC11xx\、LPC11xx(L)、LPC11Cxx系列有三種省電模式:睡眠模式、深度睡眠模式和深度掉電(Power-down)模式。以下內容包含了低功耗模式的特性和配置。

2.1.1 睡眠模式

在睡眠模式,ARM Cortex-M0 內核系統時鐘停止,指令的執行暫停,直到復位或者發生中斷。

外設功能,如果選擇SYSAHBCLKCTRL寄存器計時,在睡眠模式繼續操作,則會產生中斷,恢復處理器運行。睡眠模式取消了動態功率(用于處理器自身、存儲器系統和相關的控制器、內部總線)。處理器狀態和寄存器、外設寄存器、內部SRAM的值保持不變,引腳的邏輯電平不變。

2.1.2 深度睡眠模式

在深度睡眠模式,與睡眠模式一樣,處理器系統時鐘不可用。所有的模擬塊都掉電,除了BOD電路和看門狗震蕩器(必須在深度睡眠模式期間,在PDSLEEPCFG寄存器中選定或取消選定)。詳細內容請參考3.5部分。

深度睡眠模式取消了所有用于flash、模擬外設的電源,用于處理器自身、存儲器系統和相關控制器、內部總線的動態電源。處理器狀態和寄存器、外設寄存器以及內部SRAM的值保持不變,引腳的邏輯電平不變。

2.1.3 深度掉電模式

在濃度掉電模式,WAKEUP引腳的異常切斷了整個芯片的電源和時鐘。在深度掉電模式期間,不保留SRAM和寄存器的內容,除了少數保存在電源管理單元中的5個32位通用寄存器的數據。

在深度掉電模式下,所有的功能引腳都是三態的,除了WAKEUP引腳。

3.進入低功耗模式

這部分描述了LPC11xx、LPC11xx(L)、LPC11Cxx系列進入三種低功耗模式的機制(睡眠模式、深度睡眠模式、深度掉電模式)。

3.1 系統控制寄存器(SCR)

SCR寄存器控制進入和退出低功耗模式的特性。

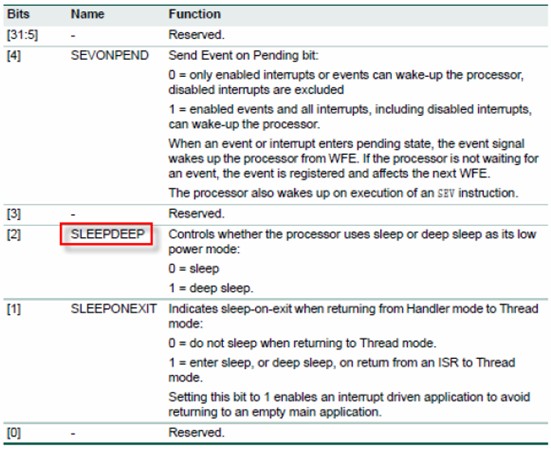

在Cortex-M0 系統控制寄存器(SCR)中,通過設置SLEEPDEEP位,進入睡眠模式和深度睡眠模式。

位描述如圖1所示。

圖1 系統控制寄存器(SCR,0xE000ED10)

在Cortex-M0系統控制寄存器(SCR)中,如果SLEEPDEEP 位是0,則是睡眠模式。

在Cortex-M0系統控制寄存器(SCR)中,如果SLEEPDEEP 位是1,則是深度睡眠模式。

3.2 電源控制寄存器(PCON)

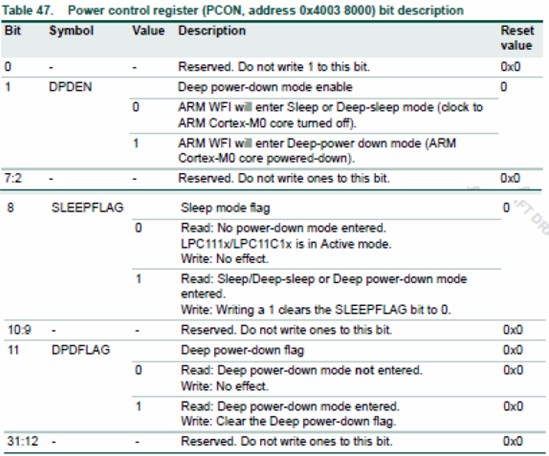

PCON寄存器選擇哪種睡眠模式(睡眠模式或深度睡眠模式),或者進入深度掉電模式。PCON分別提供了睡眠/深度睡眠模式和深度掉電模式的標志位,參看圖2。

圖2 電源模式控制寄存器

3.3 中斷等待(WFI)指令

設置完SLEEPDEEP位和PCON寄存器,執行WFI指令將直接進入低功耗省電模式。WFI指令是Cortex-M0指令,不能用ANSI C 直接訪問。CMSIS(Cortex 微控制器軟件接口標準)提供了一個內置函數,生成WFI指令,支持C編譯器。

如果C編譯器不支持WFI內置函數,用戶必須使用匯編代碼執行WFI指令。

3.4 進入睡眠模式的編程步驟

以下是進入睡眠模式的步驟:

- (1) PCON寄存器的DPDEN位必須設置為0。

- (2) ARM Cortex-M0 SCR 寄存器的SLEEPDEEP位必須設置為0。

- (3) 使用ARM Cortex-M0中斷等待指令(WFI)。

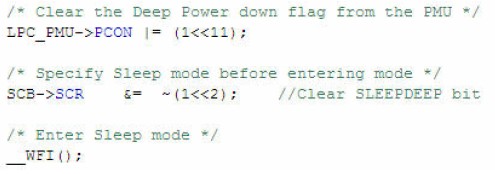

圖3為進入睡眠模式的示例代碼

圖3 示例代碼(睡眠模式)

3.5 進入深度睡眠模式的編程步驟

以下為進入深度睡眠模式的步驟:

- (1)PCON寄存器的DPDEN位必須設置為0。

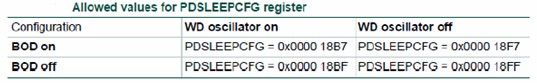

- (2)在PDSLEEPCFG寄存器深度睡眠模式下選擇電源配置。

當器件進入深度睡眠模式,這個寄存器控制看門狗震蕩器和BOD電路。在進入深度睡眠模式之前,必須至少一次使用下圖中的值初始化這個寄存器。初始化失敗,可能導致微控制器未定義錯誤。圖4所列的是PDSLEEPCFG寄存器所允許的值。

圖4 PDSLEEPCFG寄存器設置(深度睡眠模式)

- a.如果定時器需要控制自身喚醒,確保在PDRUNCFG寄存器中設置看門狗震蕩器,并在MAINCLKSEL寄存器中選擇看門狗震蕩器的時鐘源(細節請參考LPC11XX用戶手冊)。

- b.看門狗震蕩器可以運行在深度睡眠模式,為看門狗定時器或者通用定時器提供時鐘,如果它們需要自喚醒。更多細節請參考3.7部分。在這種情況下,看門狗震蕩器模擬輸出頻率必須設置為它的最低值(WDTOSCCTRL中位FREQSEL=0001,參考LPC11XX用戶手冊),進入深度睡眠模式之前,在SYSAHBCLKCTRL寄存器中設置外設時鐘為不可用(除了定時器時鐘)。如果在深度睡眠模式下運行看門狗震蕩器,將產生額外的電流損耗。

- c.如果沒有定時器自喚醒需要,且看門狗震蕩器關閉,確保在PDRUNCFG寄存器中設置對IRC的供電,并在進入深度睡眠模式前在MAINCLKSEL寄存器中為IRC選擇時鐘源。這樣能確保順利關閉系統時鐘(更多細節請參考LPC11XX用戶手冊)。

- d.在深度睡眠模式下,使能BOD電路可以在低壓下保護器件。雖然,在深度睡眠模式下,BOD電路會產生額外電流損耗。

(3) 喚醒之后,在PDAWAKECFG寄存器中選擇電源配置。可以在寄存器中對該位進行編程,以決定芯片從深度睡眠模式喚醒時進入的狀態。

(4) 如果使用外部引腳作為喚醒引腳,則在開始邏輯寄存器中使能并清除該喚醒引腳,并在NVIC中使能匹配開始邏輯的中斷。

(5) 在SYSAHBCTRL寄存器中,禁用所有的外設,除了計數器/定時器或WDT(如果需要)。

(6) 在ARM Cortex-M0 SCR 寄存器中,SLEEPDEEP位寫入1。

(7) 使用AMR Cortex-M0 中斷等待指令(WFI)。

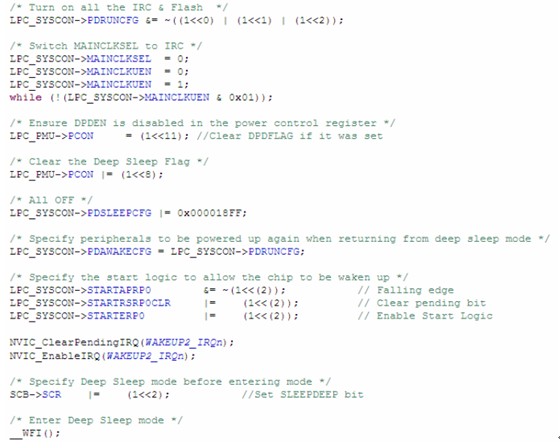

圖5為進入深度睡眠模式的示例代碼

圖5 代碼示例(深度睡眠模式)

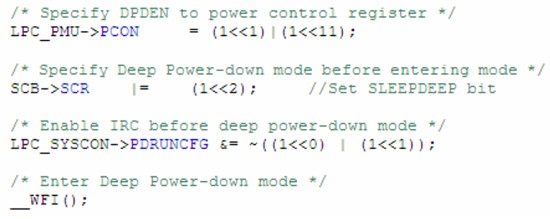

3.6 進入深度掉電模式的編程步驟

進入深度掉電模式的步驟如下:

- (1)在PCON寄存器中,DPDEN位寫入1。

- (2)保存通用寄存器中的數據(更多細節請參考LPC11XX用戶手冊)。

- (3)ARM Cortex-M0 SCR 寄存器,SLEEPDEEP位寫入1。

- (4)在進入深度掉電模式之前,在PDRUNCFG寄存器中,IRCOUT-PD和IRC-PD位寫入0,以確保對IRC供電。

- (5)使用ARM Cortex-M0 中斷等待指令(WFI)。

請注意,在進入深度掉電模式之前,WAKEUP引腳需要外部拉高。

圖6 示例代碼(深度掉電模式)

3.7 喚醒

以下部分描述了LPC11xx、LPC11xx(L)、LPC11Cxx系列每種模式的喚醒。

3.7.1.1 從睡眠模式喚醒

當NVIC 中斷或者復位發生時,自動退出睡眠模式。關于哪個中斷源與NVIC連接,請參考LPC11XX用戶手冊。中斷喚醒后,微控制器返回到最開始的電源配置狀態(由PDRUNCFG和SYSAHBCLKDIV寄存器決定)。如果發生復位,微控制器進入激活模式的默認狀態。

3.7.1.2 從深度睡眠模式喚醒

微控制器從深度睡眠模式喚醒有以下幾種方式:

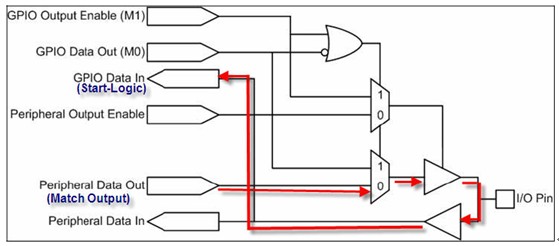

(1) 連接到開始邏輯(start logic)的外部引腳信號。某一端口引腳可以作為開始邏輯的輸入。關于有哪些端口引腳連接到開始邏輯并可作為喚醒引腳,請參考LPC11XX用戶手冊。開始邏輯不需要任何時鐘,如果在NVIC中使能從深度睡眠模式喚醒,則可以產生中斷。

(2) 開始邏輯的輸入信號(由某一通用定時器外部輸入引起的事件所產生)。引腳(保持定時器匹配功能)在NVIC中設置為開始邏輯的輸入,在SYSABHCLKCTRL寄存器中使能相應的定時器,且看門狗震撼器運行在深度睡眠模式(更多細節請參考LPC11XX用戶手冊)。當觸發了相匹配的輸入時,喚醒機制允許器件自喚醒。如圖7所示,反饋到開始邏輯,引發器件自喚醒。這種方式不需要外部觸發,減少了板上的外部元件。用這種方法所花的喚醒時間比第一種方法長。關于喚醒時間將在演示部分討論。

圖7 自喚醒框圖

(3) BOD電路復位。此時,需要在PDSLEEPCFG寄存器中使能BOD電路,且在BODCTRL寄存器中使能BOD復位(更多細節請參考LPC11XX用戶手冊)。

(4) 看門狗定時器復位。此時,看門狗震蕩器必須運行在深度睡眠模式(參看PDSLEEPCFG寄存器),且在SYSAHBCLKCTRL寄存器中使能看門狗定時器外設。

(5) 外部RESET引腳。

3.7.1.3 從深度掉電模式喚醒

拉低WAKEUP引腳從深度掉電喚醒,芯片復位。WAKEUP引腳最小脈沖寬度為50ns。

(1) 當WAKEUP引腳從高電平到低電平轉換時,喚醒有效(電平觸發)。

- a.電源管理單元(PMU)打開片上電壓調節器。當內核電壓達到電源復位(power-on-reset)跳變點,系統復位,芯片重新引導。

- b.所有寄存器(除了GPREG0-GPREG4、PCON)回到復位狀態。

(2) 一旦芯片引導完成,可以從PCON寄存器中讀取深度掉電標志位,以確認由喚醒事件引發的復位。

(3) 清除PCON寄存器深度掉電標志位。

(4) (可選)讀取通用寄存器保存的數據。

請注意,RESET引腳在深度掉電模式下沒有任何功能。

3.8 降低功耗補充材料

進一步降低電流損耗,可以考慮以下幾點:

3.8.1.1 CPU時鐘頻率

可以根據需要控制CPU時鐘頻率。

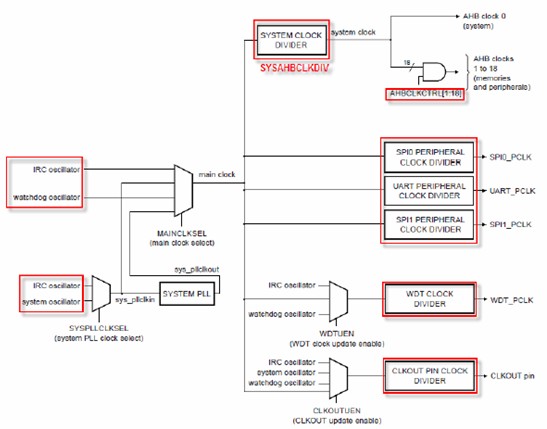

(1) 改變時鐘源:內部震蕩器(12MHz +/-1%)、系統震蕩器(1MHz to 25MHz),看門狗震蕩器(7.8kHz to 1.7MHz +/-40%)。

(2) 重設PLL的值,和/或變更AHB Clock Divider(SYSAHBCLKDIV)的值。

(3) 降低PLL輸出頻率(FCCO,156MHz to 320MHz)可以降低功耗。

(4) 8位系統AHB Clock divider寄存器(SYSAHBCLKDIV)可以降低CPU的操作到某一低的頻率,臨時降低功耗而無需關閉SYS PLL。見圖8所示。

圖8 時鐘發生單元(CGU)框圖

3.9 系統AHB 時鐘控制寄存器(AHBCLKCTRL)

如圖8所示,SYSAHBCLKCTRL寄存器使能系統和外充模塊的時鐘。根據需要,用戶可以使用該寄存器禁用未使用的外設時鐘,以達到降低功耗的目的。更多細節請參考LPC11XX用戶手冊。

3.10 外設時鐘除法器

選定的外設有各自的時鐘除法器(SPI0CLKDIV,UARTCLKDIV,SPI1CLKDIV,WDTCLKDIV,CLKOUTDIV),可以控制提供給相應外設的時鐘信號的頻率(見圖8)。根據實際需要,用戶可以使用除法器降低外設時鐘頻率或者關閉時鐘以降低功耗。更多細節請參考LPC11XX用戶手冊。

3.11 掉電配置寄存器(PDRUNCFG)

PDRUNCFG 寄存器包含模擬塊電源開關的控制位,通過模擬外設可以消除電源消耗。更多細節請參考LPC11XX用戶手冊。

3.12 其他

3.12.1 軟件

大部分嵌入式應用都以while(1) loop 結束,用于中斷。此時,仍然從片上flash獲取代碼并執行,增加了功耗。一種較好的解決方案是選擇睡眠省電模式,并等待中斷。外設的中斷可以把器件從睡眠模式喚醒。內核在等待中斷時保持睡眠模式,可以有效的降低功耗。

3.12.2 端口引腳

可以增加一些步驟,在低功耗模式下降低電流損耗。LPC11xx、LPC11xx(L)、LPC11Cxx系列的通用端口引腳,默認可編程內部拉高。在進入低功耗模式之前,可以通過以下幾種方法降低IO的電流:

(1) 所有通用I/O引腳(GPIO)默認帶有輸入上拉電阻。首先,使用IOCON寄存器,禁用所有通用端口引腳內部上拉(pull-ups)。其次,設置I/O為GPIO輸出,低電平。確保引腳沒有外部拉高。

(2) 所有通用I/O引腳(GPIO)默認帶有輸入上拉電阻。首先,使用IOCON寄存器,禁用所有通用端口引腳內部上拉(pull-ups)。其次,設置I/O為GPIO輸出,高電平。確保引腳沒有外部拉低。

(3) 使用IOCON寄存器,首先,禁用所有通用端口引腳內部上拉(pull-ups)。其次,設置I/O為GPIO輸入且使用外部電阻,把I/O拉高或拉低。

請注意,在深度睡眠模式,端口引腳的狀態不影響電流的損耗,以上提到的方法在這個模式下無需考慮。

3.12.3 CAN引腳

LPC11C1x器件,如果不使用CAN部件,CAN引腳(CAN-RXD和CAN-TXD)建議外部拉低,以降低IO電流。

3.12.4 RESET-N/PIO0-0引腳

LPC11xx、LPC11xx(L)、LPC11Cxx,在深度掉電模式時,RESET/PIO0-0引腳需要通過外部10K-47K電阻拉高。如果引腳懸空,用戶可以看到電流損耗的增加。

3.12.5 調試

用戶應該知道的關于一些調度的限制。最重要的是,由于Cortex-M0集成方面的一些限制,LPC11xx、LPC11xx(L)、LPC11Cxx在一般方式下,不能從睡眠、深度睡眠和深度掉電模式下喚醒。建議不要在這些模式下調試。一旦通過SWD接口下載應用程序,USB和SWD之間的適配器要從板上移除。另一個問題是,調式模式改變了Cortex-M0 CPU處理降低功耗模式的方式。這將導致器件級的電源模式不同于通常模式下的操作。這些不同,意味著在調試時不能測試電源;在應用中,測試結果將比通常操作時要高。

4.低功耗模式演示

5.總結

下載完整PDF文檔:

LPCXpresso環境下的LPC1100低功耗模式和喚醒時鐘.PDF

LPCXpresso環境下的LPC1100低功耗模式和喚醒時鐘.PDF